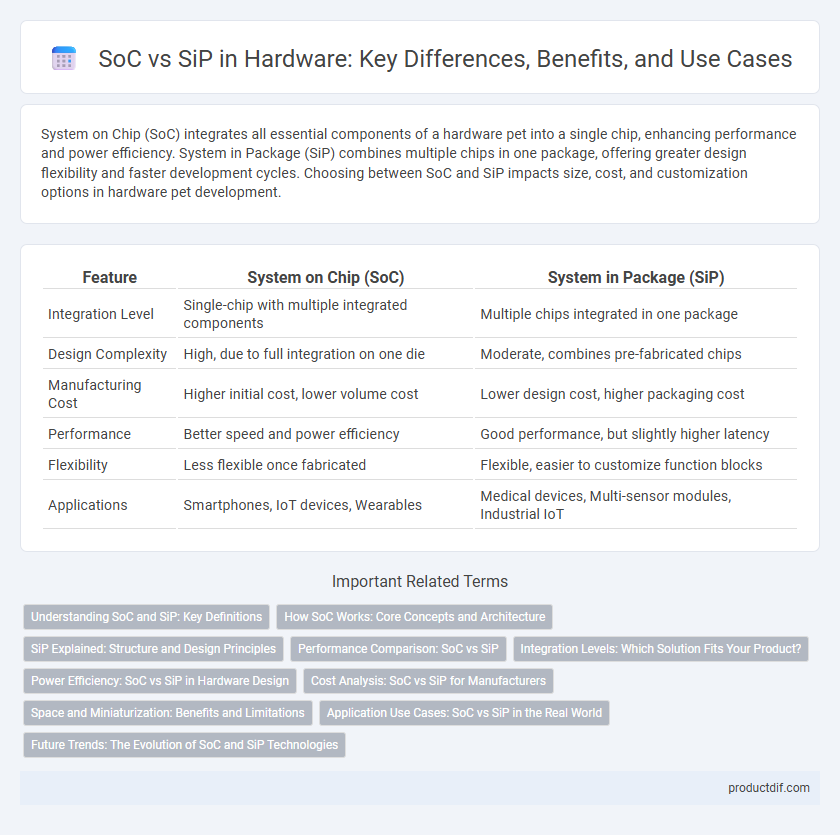

System on Chip (SoC) integrates all essential components of a hardware pet into a single chip, enhancing performance and power efficiency. System in Package (SiP) combines multiple chips in one package, offering greater design flexibility and faster development cycles. Choosing between SoC and SiP impacts size, cost, and customization options in hardware pet development.

Table of Comparison

| Feature | System on Chip (SoC) | System in Package (SiP) |

|---|---|---|

| Integration Level | Single-chip with multiple integrated components | Multiple chips integrated in one package |

| Design Complexity | High, due to full integration on one die | Moderate, combines pre-fabricated chips |

| Manufacturing Cost | Higher initial cost, lower volume cost | Lower design cost, higher packaging cost |

| Performance | Better speed and power efficiency | Good performance, but slightly higher latency |

| Flexibility | Less flexible once fabricated | Flexible, easier to customize function blocks |

| Applications | Smartphones, IoT devices, Wearables | Medical devices, Multi-sensor modules, Industrial IoT |

Understanding SoC and SiP: Key Definitions

System on Chip (SoC) integrates multiple components like CPU, GPU, memory, and I/O interfaces onto a single semiconductor die, enhancing performance and reducing power consumption for devices such as smartphones and tablets. System in Package (SiP) packs multiple integrated circuits die, including SoCs, memory, and sensors, within a single module, offering design flexibility and compactness suitable for wearable technology and IoT devices. Understanding SoC and SiP involves recognizing SoC as a single-chip solution optimizing integration, while SiP combines multiple chips in one package, enabling complex functionality in limited space.

How SoC Works: Core Concepts and Architecture

A System on Chip (SoC) integrates multiple components such as the CPU, GPU, memory, and input/output interfaces on a single semiconductor substrate, enabling efficient communication and reduced latency. Its architecture typically features a centralized processing core with shared system buses and dedicated modules for specialized functions, optimizing power consumption and performance. High-level integration in SoCs supports compact hardware design, making them ideal for smartphones, tablets, and embedded systems.

SiP Explained: Structure and Design Principles

System-in-Package (SiP) integrates multiple heterogeneous components, such as processors, memory, and sensors, into a single compact module, optimizing space and power efficiency. SiP architecture utilizes advanced packaging techniques like through-silicon vias (TSVs) and wafer-level packaging to enhance interconnect density and signal integrity. This design principle enables versatile, high-performance solutions for applications demanding miniaturization and multifunctionality, surpassing traditional System-on-Chip (SoC) integration limits.

Performance Comparison: SoC vs SiP

System on Chip (SoC) integrates all components on a single silicon die, leading to superior performance through faster interconnects and lower power consumption compared to System in Package (SiP), which combines multiple integrated circuits in a single package. SoCs generally offer higher processing speed and energy efficiency due to reduced signal latency and optimized component communication. SiPs provide flexibility and heterogeneous integration but may experience performance bottlenecks caused by inter-chip communication overhead and thermal constraints.

Integration Levels: Which Solution Fits Your Product?

System on Chip (SoC) integrates multiple components such as CPU, memory, and peripherals onto a single silicon die, offering high performance and compact design ideal for devices requiring fast processing and low power consumption. System in Package (SiP) combines several integrated circuits and passive components within a single package, providing flexible integration suitable for multi-functionality and rapid development cycles. Choosing between SoC and SiP depends on factors like product complexity, development time, cost constraints, and specific performance requirements.

Power Efficiency: SoC vs SiP in Hardware Design

System on Chip (SoC) designs enhance power efficiency by integrating multiple components into a single silicon die, reducing inter-component communication energy and minimizing overall power leakage. System in Package (SiP) solutions, while enabling heterogeneous integration of diverse technologies, often incur higher power consumption due to longer interconnect paths and packaging overhead. Optimizing power efficiency in hardware design requires evaluating SoC for lower energy per operation, whereas SiP offers flexibility at the potential cost of increased power dissipation.

Cost Analysis: SoC vs SiP for Manufacturers

System on Chip (SoC) typically offers lower per-unit manufacturing costs due to integration of multiple components into a single silicon die, reducing packaging and assembly expenses. System in Package (SiP) incurs higher costs from integrating multiple dies and components within a single module, which increases complexity in interconnects and testing. Manufacturers must weigh SoC's upfront design and fabrication expenses against SiP's flexibility and faster time-to-market when evaluating overall cost efficiency.

Space and Miniaturization: Benefits and Limitations

System on Chip (SoC) offers significant space savings by integrating multiple components into a single silicon die, enabling high miniaturization ideal for compact devices like smartphones and wearables. System in Package (SiP) stacks or places discrete chips within a single package, providing flexibility for heterogeneous integration but often occupying more board space compared to SoCs. SoCs optimize power efficiency and performance in minimal footprint, while SiPs facilitate rapid design iterations and multi-technology integration at the cost of larger space utilization.

Application Use Cases: SoC vs SiP in the Real World

System-on-Chip (SoC) solutions dominate in smartphones and automotive applications where compact, high-performance integration is critical, offering low power consumption and optimized processing capabilities. System-in-Package (SiP) is preferred in wearable devices and IoT sensors due to its flexibility in combining heterogeneous components, enabling multi-functional compact modules with faster time-to-market. Real-world use cases demonstrate SoC's strength in large-scale integration for mass production, while SiP excels in custom, space-constrained applications requiring diverse technology integration.

Future Trends: The Evolution of SoC and SiP Technologies

The evolution of SoC (System on Chip) and SiP (System in Package) technologies is driven by the demand for higher performance, energy efficiency, and miniaturization in hardware design. Future trends indicate a shift towards heterogeneous integration, where combining multiple specialized dies in a single package enhances functionality and flexibility beyond traditional monolithic SoC architectures. Advanced packaging techniques like 3D stacking and chiplet architectures will further blur the distinction between SoC and SiP, enabling more scalable and customizable hardware solutions for AI, 5G, and IoT applications.

SoC vs SiP Infographic

productdif.com

productdif.com